Tag: eFPGA

CLEAR is Customizable and Programmable ASIC by ChipIgnite

Efabless has launched a 100% open-source FPGA chip CLEAR, built on Caravel - an open-source ASIC platform provided as a base (SoC) and offering an end-to-end open design, right down to the CPU core. The explanation of the product is simple and quite relatable to the maker's community -...

Continue Reading

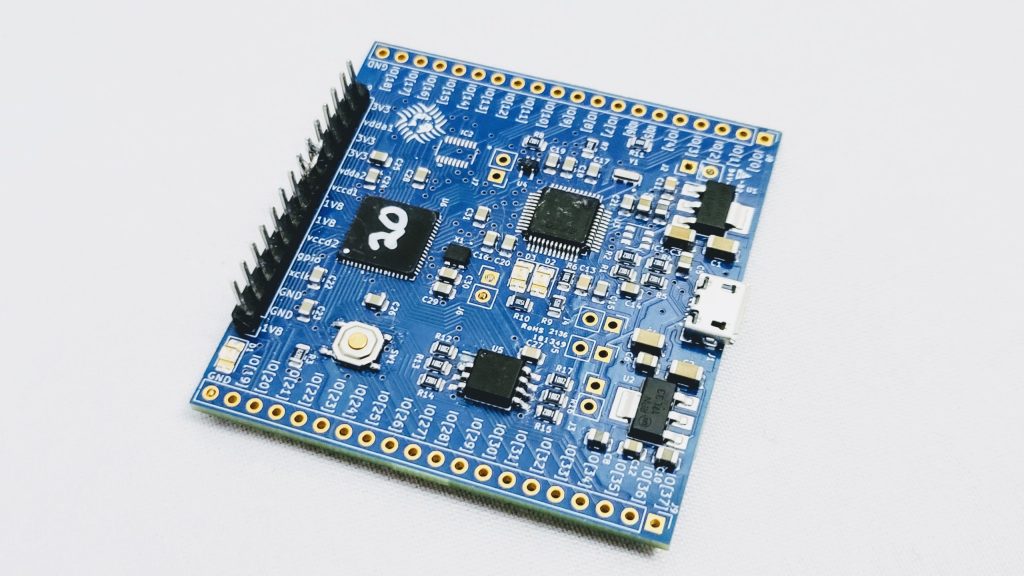

SparkFun QuickLogic Thing Plus featuring EOS S3 MCU and eFPGA is now available at $45.95

SparkFun QuickLogic Thing Plus was originally crowdfunded on CrowdSupply that raised around $4500. If you did not back the product back then, no worries, you can buy it now on the SparkFun product page. SparkFun QuickLogic Thing Plus is a powerful FPGA board that comes with a...

Continue Reading

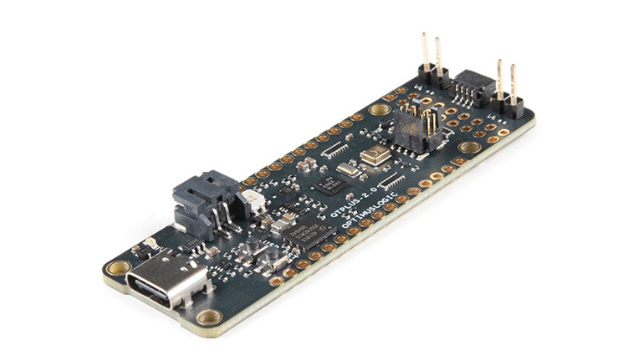

QuickLogic Launches Qomu – an Open Source SoC Dev Kit That Fits in Your USB Port

QuickLogic Corporation, a developer of ultra-low power multi-core voice-enabled SoCs, embedded FPGA IP, and endpoint AI solutions, today announced the introduction of its new Qomu development kit, a tiny form factor Arm® Cortex®-M4F MCU + eFPGA combination that fits into a USB Type A...

Continue Reading

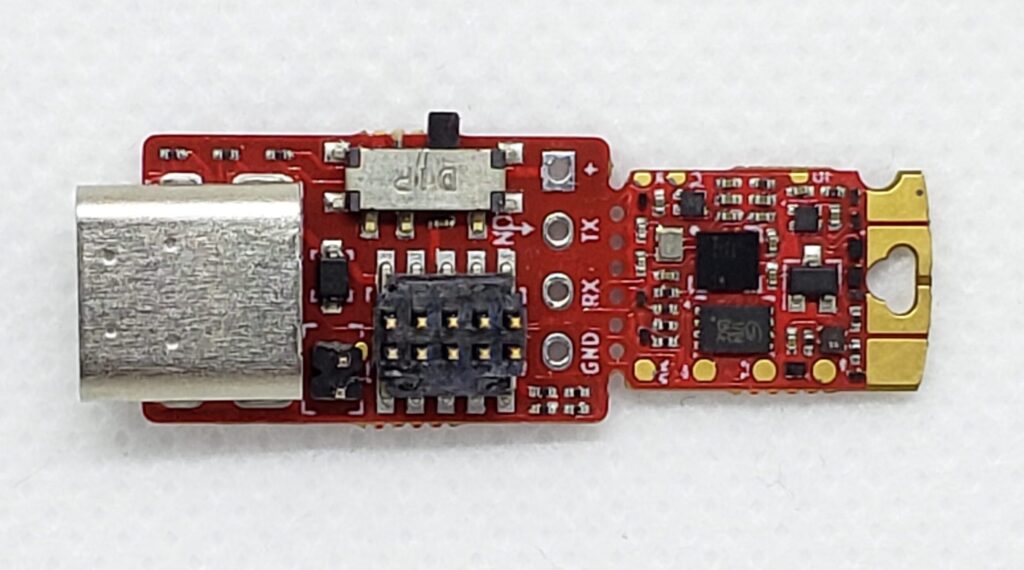

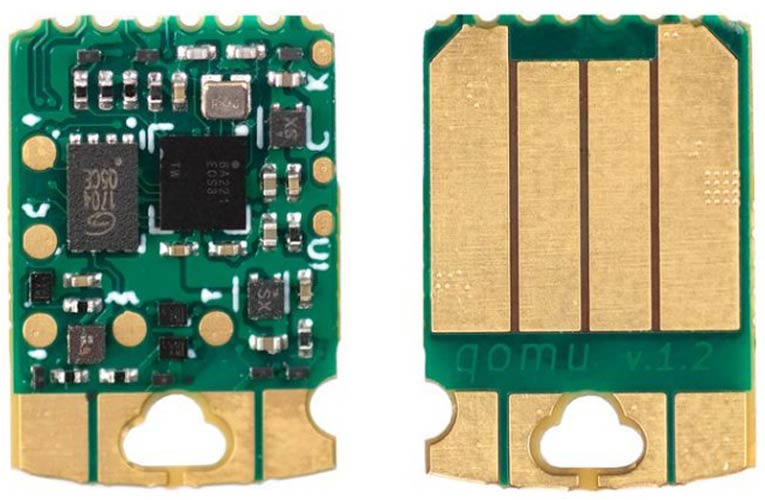

Meet Qomu – A complete SoC that easily fits inside a USB port

Tomu family of USB devices has recently introduced a small form factor board that is not only a single MCU or an FPGA, but a complete System-on-chip that fits easily inside a USB port. The tiny compact board called Qomu, is a capable USB device that integrates an EOS S3 low-power MCU...

Continue Reading

Taking Advantage of Embedded FPGA (eFPGA)

By Geoff Tate, CEO of Flex Logix, Inc. Whether you are designing an SoC, MCU or other chip, the one common heartache is “freezing RTL.” Up until that point, it’s no problem making a change or update, but once it’s frozen, the chip design is “locked in.” A change after that...

Continue Reading

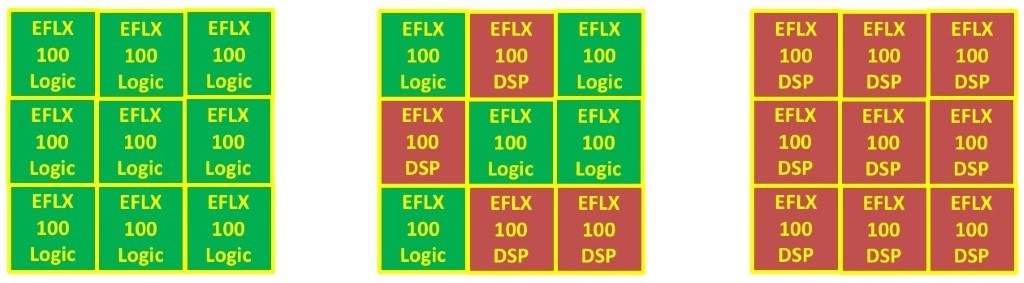

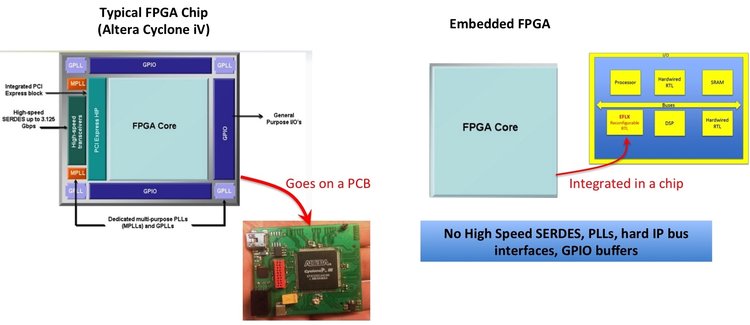

What is Embedded FPGA — Known as eFPGA

Today’s market requirements change faster than the typical development time for a new device or the ability of designers of SoCs to know. To solve this problem, FPGAs/MCUs are used so developers can change the configuration/firmware later. As known, MCU IP is static and you can't...

Continue Reading