OpenHW Group introduces RISC-V powered CORE-V microcontroller development kit

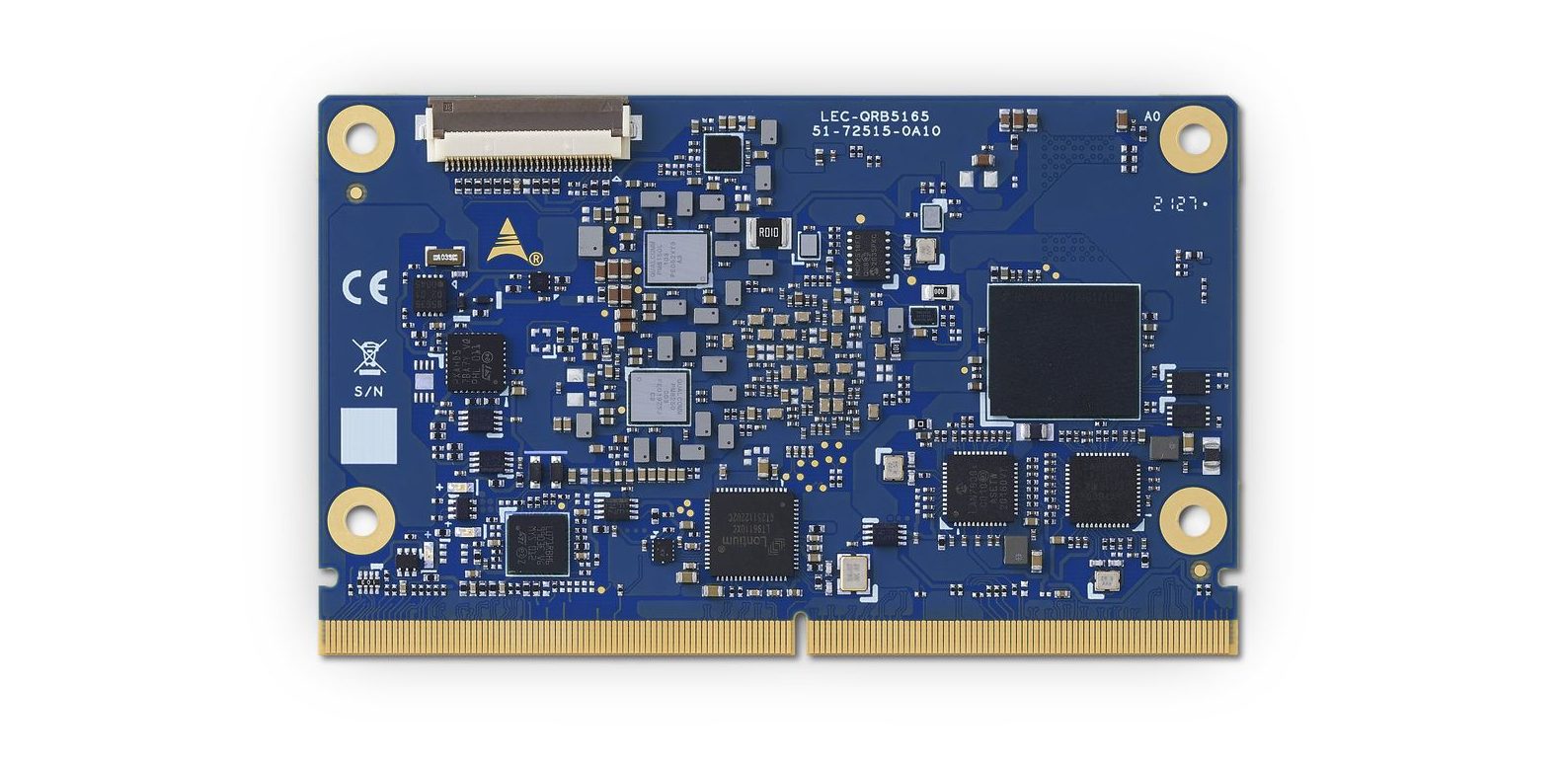

Ottawa-based RISC-V working group, OpenHW Group, has announced a RISC-V powered CORE-V microcontroller development kit for IoT and AI-driven applications. The hardware features the inhouse OpenHW CORE-V microcontroller, a CORE-V software developer kit and an open PCB designed to support Amazon Web Services through AWS IoT ExpressLink. The CORE-V SDK has integrated the Eclipse development environment as well.

The CORE-V microcontroller development kit is based on the open-source CV32E40P embedded-class processor, a 32-bit efficient RISC-V processor core with a four-stage pipeline that implements the RV32IM[F]C instruction extensions. If you are new to the RISC-V instruction set architecture, the RV32I is the base instruction with M and C as the extensions and optional F extensions.

“The enormous potential of IoT applications requires new ways of thinking about design, and the open-source community is delivering hardware, software and development tools to accelerate innovation,” said Rick O’Connor, President and CEO of OpenHW Group. “It’s truly inspiring to see such a cohesive global collaborative engineering effort to develop open-source building blocks enabling embedded MCU designs.”

At Embedded World 2022, the RISC-V working group showcased the CORE-V microcontroller development kit to emulate weather station sensors located in the exhibition hall and several global locations. The demonstration includes the CORE-V MCU, CORE-V SDK, IoT sensors interconnection, and an AWS application.

The CORE-V microcontroller board is fabricated by GlobalFoundries’ using 22FDX process technology for efficient integration of digital and analogue signals, delivering high performance for low-power applications. The design and verification of the CV32E40P processor involved key contributions from Imperas, Siemens EDA, SiLabs and several others. The core is based on the PULP Platform RI5CY core, originally developed at ETHZ’s Integrated Systems Laboratory (IIS) and the Energy-efficient Embedded Systems (EEES) group of the University of Bologna.

For computing complex artificial intelligence and machine learning workloads, the CORE-V MCU includes a QuickLogic eFPGA to accelerate the processing from the CV32E40P processor. Imperas has released riscvOVPsimCOREV for free, simulating the CORE-V MCU with Imperas reference models used to verify the CV32E40P.

“This project highlights the open-source collaborative development of industry-grade CORE-V processor IP with supporting hardware and software by a wide spectrum of members within the OpenHW community.”

CORE-V MCU DevKit is currently under pre-launch on GroupGets for early access campaign manufacturing and shipping.