RISC-V, an open-source instruction-set architecture based on RISC instructions is projected to be the architecture of the future. As RISC-V architecture evolves, there is a need for a high-performance RISC-V simulator. MachineWare, a Germany-based startup known for its high-speed instruction set simulators, has unveiled SIM-V, a RISC-V simulator. This simulator allows developers to interactively debug even the most complex designs without requiring actual hardware.

Being MachinWare’s flagship product, SIM-V blends an immensely strong simulation experience with great customizability for every application varying from tiny embedded devices to large supercomputers. This simulator enables developers to test software stacks in real-time including Kernel OS, Java virtual machines or rich graphical environments, and other complex user-space applications. It offers less execution time, saves compute resources, and fosters developers to work fast.

SIM-V Variants

In order to perfectly match the user’s requirements, MachineWare offers two specialized SIM-V variants. The two variants are SIM-V Compute and SIM-V Edge.

SIM-V Compute

SIM-V Compute aims for designing and developing 64bit RISC-V systems. These systems are mainly focused to execute complex software stacks with a rich OS and powerful APIs. This simulator makes it simple to detect hard-to-find bugs and other software issues.

Features of SIM-V Compute:

- SIM-V Compute interacts with developer-friendly industry-standard debugging tools in addition to its extensive introspection and debugging capabilities. As a result, a user may readily identify bugs and other security glitches inside the software stack.

- It provides smooth operation and an interactive user experience while simulating complex software stacks.

- Due to its configurable architecture, a developer may combine different processor designs to develop a multi-core system without degrading the performance.

- Integration of SIM-V has become easy with the support of the SystemC TLM-2.0 standard (IEEE 1666-2011).

SIM-V Edge

Small, embedded devices living at the cloud’s edge characterize the modern world. These devices rely on interconnectivity to function effectively but also they are more likely to face security issues. It makes designing and developing a secure 32-bit RISC-V edge computing device convenient.

Features of SIM-V Edge:

- With this variant, a developer may quickly interface a wide range of virtual and physical hardware.

- A developer can discreetly monitor and track the hardware condition during the operation.

- It includes a fault injection mechanism for locating major software defects and security glitches.

- The support of SystemC TLM-2.0 standard (IEEE 1666-2011) allows easy integration of SIM-V Edge.

Technologies Powering the High-Performance SIM-V

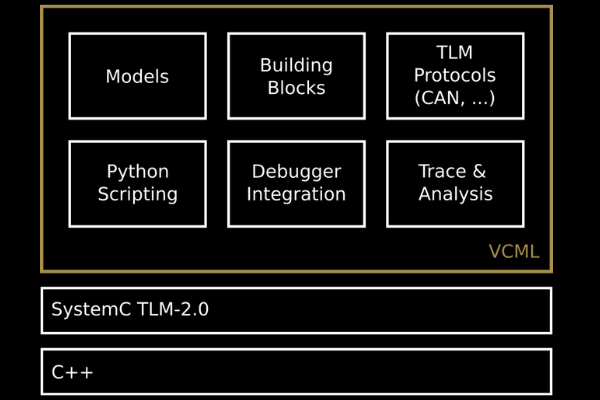

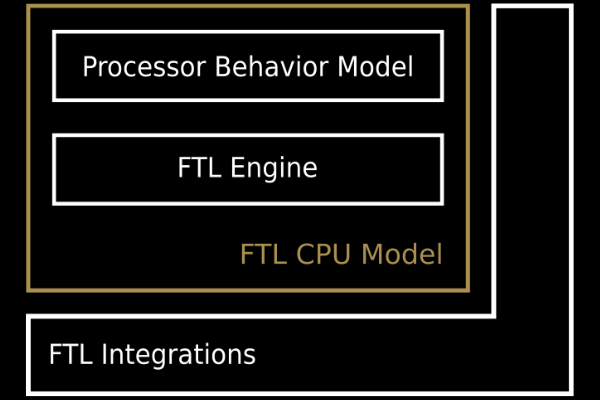

Using MachineWare’s innovative core technology, SIM-V provides maximum performance and seamless model integration. This powerful RISC-V simulator is based on MachineWare’s open-source SystemC modelling library VCML and also the fast and flexible instruction set simulation framework FTL.

VCML (Virtual Components Modeling Library)

VCML is MachineWare’s free and open-source (Apache 2.0) SystemC TLM-2.0 modeling library. It comprises a set of off-the-shelf models for frequently utilized components like buses, memory, timers, and I/O controllers such as Ethernet, PCI/e, and VIRTIO. VCML enables simple integration into current setups and SystemC platform models, with tracing, analysis, and scripting tools.

FTL (Fast Translator Library)

FTL is MachineWare’s approach for delivering high-performance, retargetable, and functional Instruction Set Simulators (ISSs). This enables easy customization of the simulator to incorporate custom-tailored RISC-V instruction set extensions or even construct entirely unique instruction set simulators for any microprocessor architecture.

The managing director and co-founder of MachineWare, Lukas Jünger commented on the aim of the robust simulator in a press release

“Our objective is to provide RISC-V software developers with the tools they require to produce safe and secure software stacks on time and without glitches.”

The technologies powering SIM-V makes it one of the high-performance simulator. Coming with a best-in-class high simulation engine along with a rugged architecture, it allows a developer to perform smooth operations. For more information on the library or the SIM-V variants visit the official webpage.