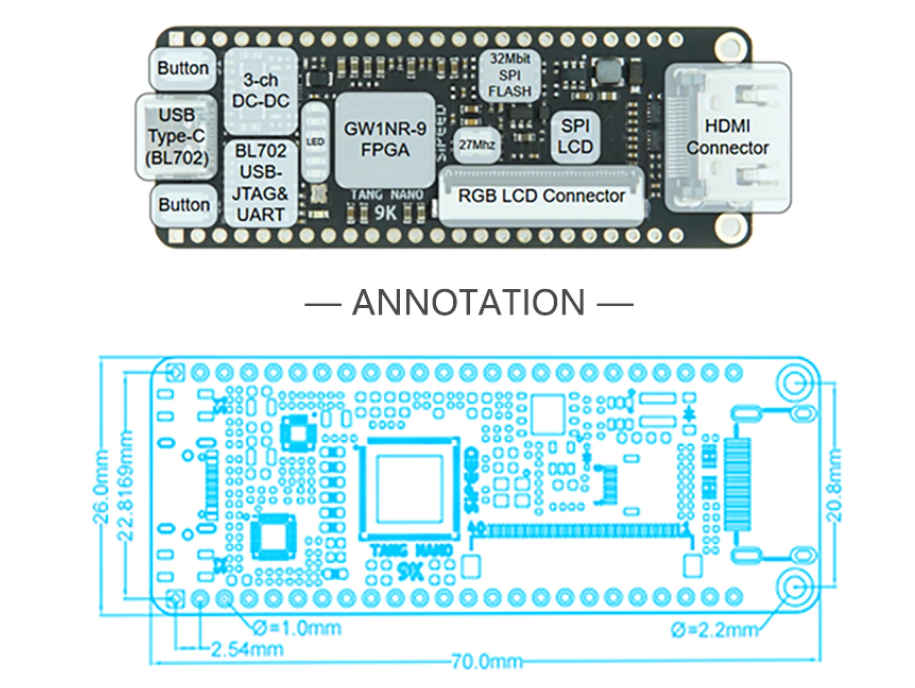

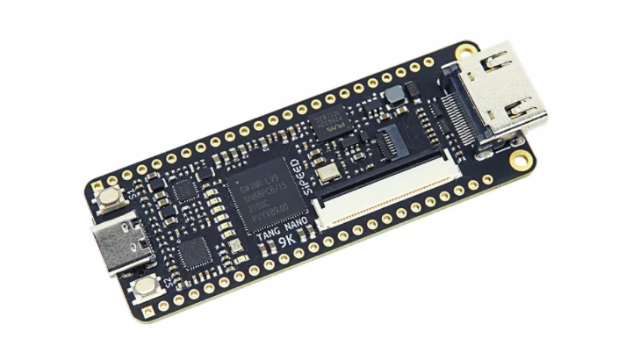

Sipeed Introduces Tang Nano 9K FPGA board, Compatible with RISC-V softcore PicoRV

Sipeed has surprisingly introduced yet another Tang Nano FPGA board based on the Gowin GW1NR-9 chip. This time, the manufacturer has pushed the limits to around 9K (8640) logic units (LUT4), unlike the predecessor Tang Nano 1K and Tang Nano 4K with around 1152 and 4608 LUTs respectively. Despite the hardcore Arm Cortex-M3 processor embedded inside the Tang Nano 4K, Sipeed decided not to go ahead with that design for the latest hardware release.

As mentioned above, Tang Nano 9K is built around the Gowin GW1NR-9 FPGA chip featuring 6480 flip flops and an extended DRAM of 64Mbit. Being one of the entry-level FPGA-kit for RISC-V developers, the hardware comes with tightly integrated 32Mbit of flash storage for your example code and is expandable via MicroSD card. For experimentation, RISC-V softcore PicoRV is also available for developers, which can be accessed through the official GitHub repository. Furthermore, the manufacturer has provided community access to the PicoRV projects running on the newly launched Tang Nano 9K FGPA board. Now, let us take a look at the specifications.

Specifications of Tang Nano 9K FPGA Board

- FPGA Module: GOWIN LittleBee GW1NR-9

- LUTs: 8640

- Flip-flop: 6480

- SSRAM: 17280 bits

- BSRAM: 468 bits

- SDRAM: 64 Mbits

- pSRAM: 64-128 Mbits

- PLLs: 2

- Memory: 32Mbit SPI flash memory with MicroSD card slot

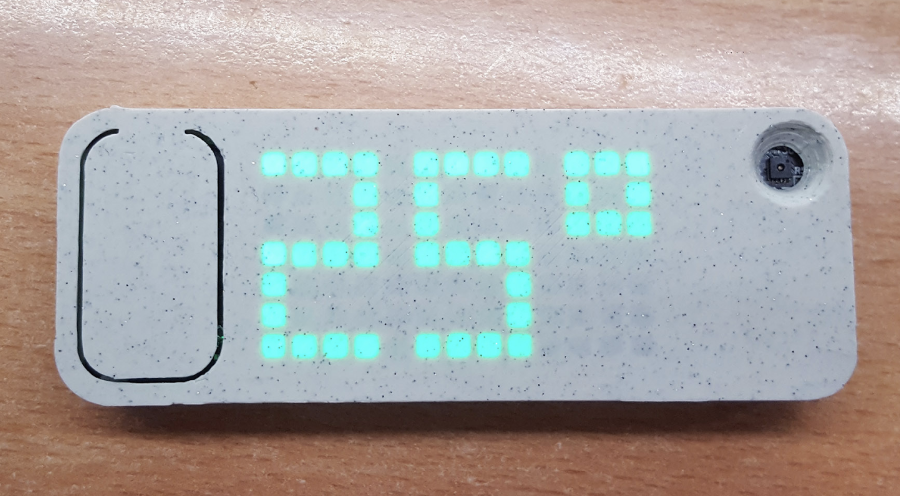

- Display interfaces: HDMI port, RGB interface connector and SPI interface

- USB ports: USB Type-C port for power and JTAG programming

- Buttons: Onboard 2 user buttons

- LEDs: Onboard 6 LEDs

- Connectors: 2x 24-pin GPIOs, SPI and HDMI

- Power: 5V via USB connector

- Dimensions: Approximately 65×23 mm

Note that some of the specifications of the hardware have been taken from CNX-Software.

To get started with the FPGA board, the hardware is developed using the Gowin development environment which supports general hardware description languages like Verilog and C/C++. If you plan to use RISC-V soft-core PicoRV, then the user is recommended to use Verilog HDL to write custom hardware functions and use C language for code running on the core. For this, the experience level of a senior engineer is expected. If you are a beginner as an FPGA developer, then the user can use HDL like Verilog to design simple logic circuits.

If you are interested in purchasing Tang Nano 9K FPGA board, head to the product store page on AliExpress, priced at $14.99 for the base model.